- 您现在的位置:买卖IC网 > Sheet目录2098 > MK2069-01GILFTR (IDT, Integrated Device Technology Inc)IC VCXO CLK SYNCHRONIZER 56TSSOP

MK2069-01

VCXO-BASED LINE CARD CLOCK SYNCHRONIZER

VCXO AND SYNTHESIZER

IDT VCXO-BASED LINE CARD CLOCK SYNCHRONIZER

18

MK2069-01

REV K 051310

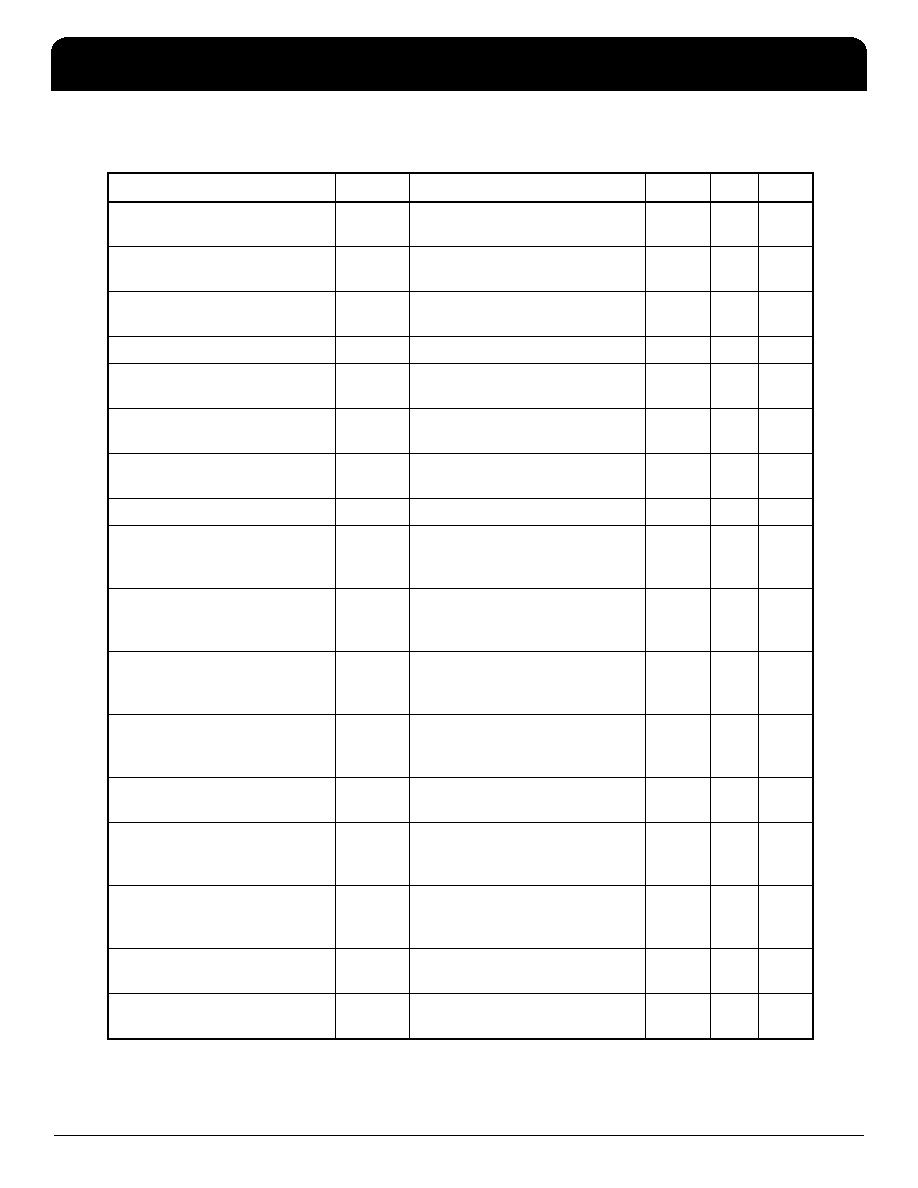

AC Electrical Characteristics

Unless stated otherwise, VDD = 3.3V ±5%, Ambient Temperature -40 to +85

° C

Parameter

Symbol

Conditions

Min.

Typ.

Max. Units

VCXO Crystal Frequency Range

(Note 1)

fXTAL

Using recommended

crystal

13.5

27

MHz

VCXO Crystal Pull Range

fXP

Using recommended

crystal

±115

±150

ppm

VCXO Crystal Free-Run

Frequency (Note 2)

fXF

Input reference = 0 Hz

-300

-150

ppm

Input Clock Frequency (Note 2)

fI

0.001

170

MHz

Input Clock Pulse Width

tID

Positive or Negative

Pulse

10

nsec

VCXO PLL Phase Detector

Frequency (Note 3)

fPD

0.001

27

MHz

VCXO PLL Phase Detector Jitter

Tolerance

tJT

1 UI = phase detector

period

0.4

UI

Translator PLL VCO Frequency

fV

40

320

MHz

Timing Jitter, Filtered

500Hz-1.3MHz (OC-3)

tOJf

Derived from phase

noise characteristics,

peak-to-peak 6 sigma

95

ps

Timing Jitter, Filtered

65kHz-5MHz (OC-3)

tOJf

Derived from phase

noise characteristics,

peak-to-peak 6 sigma

85

ps

Timing Jitter, Filtered

1kHz-5MHz (OC-12)

tOJf

Derived from phase

noise characteristics,

peak-to-peak 6 sigma

105

ps

Timing Jitter, Filtered

250kHz-5MHz (OC-12)

tOJf

Derived from phase

noise characteristics,

peak-to-peak 6 sigma

80

ps

Output Duty Cycle (% high time),

VCLK when SV Divider = 1

tOD

Measured at VDD/2,

CL=15pF

40

50

60

%

Output Duty Cycle (% high time),

VCLK when SV Divider > 1,

TCLK

tOD

Measured at VDD/2,

CL=15pF

44

50

65

%

Output High Time, RCLK

(Note 4)

tOH

Measured at VDD/2,

CL=15pF

0.5

VCLK

Period

Output Rise Time, VCLK and

RCLK

tOR

0.8 to 2.0V, CL=15pF

1.5

2

ns

Output Fall Time, VCLK and

RCLK

tOF

2.0 to 0.8V, CL=15pF

1.5

2

ns

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MK2069-04GILFTR

IC VCXO CLK TRANSLATOR 56-TSSOP

MK2302S-01LFTR

IC MULTIPLIER/ZD BUFFER 8-SOIC

MK2304S-2LF

IC PLL ZD BUFFER LO SKEW 8-SOIC

MK2703SILF

IC PLL AUD CLK SYNTHESIZER 8SOIC

MK2704SLF

IC PLL AUD CLK SYNTHESIZER 8SOIC

MK2716SLFTR

IC CLK SYNTHESIZER HDTV 8-SOIC

MK2732-06GLF

IC VCXO/MULTIPLIER 16-TSSOP

MK2745-21SLFTR

IC CLK SOURCE DVD/MPEG 16-SOIC

相关代理商/技术参数

MK2069-01GITR

功能描述:IC VCXO CLK SYNCHRONIZER 56TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:*

MK2069-03

制造商:ICS 制造商全称:ICS 功能描述:VCXO-Based Clock Translator with High Multiplication

MK2069-03GI

功能描述:IC VCXO CLK TRANSLATOR 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件

MK2069-03GITR

功能描述:时钟发生器及支持产品 VCXO-BASED CLOCK TRANSLATOR RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56

MK2069-04

制造商:ICS 制造商全称:ICS 功能描述:VCXO-Based Universal Clock Translator

MK2069-04GI

功能描述:IC VCXO CLK TRANSLATOR 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:*

MK2069-04GILF

功能描述:时钟发生器及支持产品 VCXO-BASED UNIVERSAL CLOCK TRANSLATOR RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56

MK2069-04GILFTR

功能描述:时钟发生器及支持产品 VCXO-BASED UNIVERSAL CLOCK TRANSLATOR RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56